Die Illusion des unendlichen Speichers

Im Kern dreht sich bei virtuellem Speicher alles um die Schaffung einer Illusion – der Illusion, mehr Speicher zu haben, als physisch vorhanden ist. Aber wie funktioniert dieser Zaubertrick?

Einführung: Seitentabellen

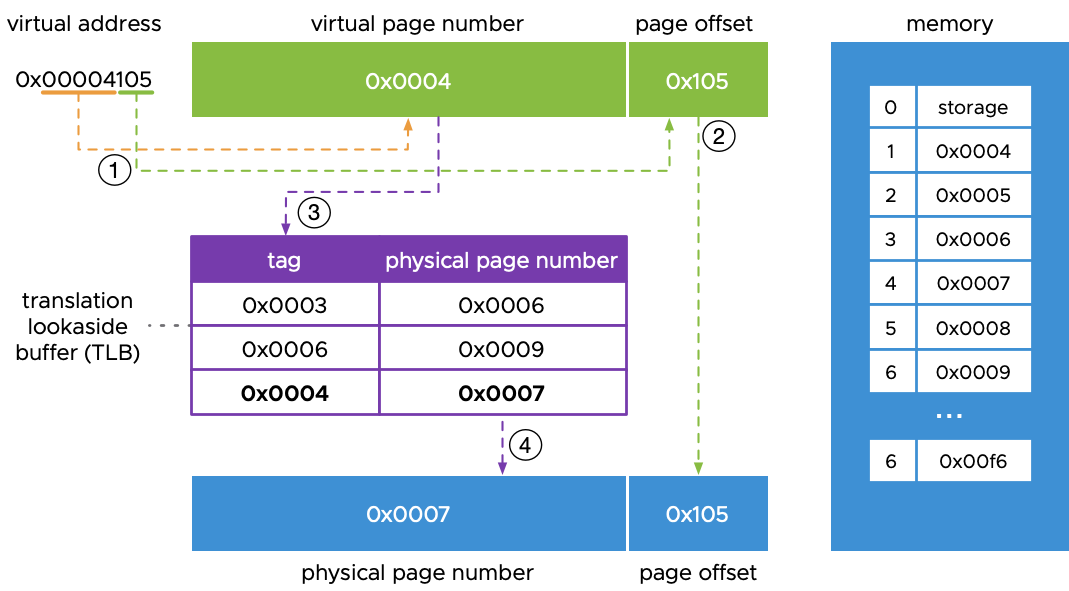

Seitentabellen sind die stillen Helden des Speichermanagements. Sie fungieren als Karte, die zwischen der weiten Welt der virtuellen Adressen und dem begrenzten Bereich des physischen Speichers übersetzt. Hier ist eine vereinfachte Darstellung, wie sie funktionieren:

struct PageTableEntry {

uint32_t physical_page_number : 20;

uint32_t present : 1;

uint32_t writable : 1;

uint32_t user_accessible : 1;

uint32_t write_through : 1;

uint32_t cache_disabled : 1;

uint32_t accessed : 1;

uint32_t dirty : 1;

uint32_t reserved : 5;

};

Jeder Eintrag in der Seitentabelle entspricht einer Seite im virtuellen Speicher, typischerweise 4KB groß. Wenn ein Programm versucht, auf Speicher zuzugreifen, verwendet die CPU die Seitentabelle, um herauszufinden, wo dieser Speicher tatsächlich im physischen RAM liegt.

Die Kosten der Übersetzung

Aber hier ist der Haken: Die Übersetzung von Adressen über Seitentabellen ist langsam. Wirklich langsam. Wir sprechen von "Farbe beim Trocknen zusehen"-langsam. Für jeden Speicherzugriff müsste die CPU mehrere Speicherabfragen durchführen, nur um herauszufinden, wo die tatsächlichen Daten gespeichert sind. Hier kommt unser nächster Akteur ins Spiel...

TLBs: Die Geschwindigkeitsdämonen der Adressübersetzung

Translation Lookaside Buffers, oder TLBs, sind das Lachgas in unserem virtuellen Speicher-Motor. Sie sind kleine, schnelle Caches, die kürzlich erfolgte Übersetzungen von virtuellen zu physischen Adressen speichern.

Stellen Sie sich TLBs als das Kurzzeitgedächtnis Ihres Gehirns für Wegbeschreibungen vor. Anstatt jedes Mal eine Karte (Seitentabelle) herauszuholen, wenn Sie irgendwohin wollen, merken Sie sich einfach die Route, wenn Sie kürzlich dort waren.

Wie TLBs ihren Zauber wirken

Hier ist ein vereinfachter Pseudocode, wie ein TLB funktionieren könnte:

def access_memory(virtual_address):

if virtual_address in TLB:

physical_address = TLB[virtual_address]

return fetch_data(physical_address)

else:

physical_address = page_table_lookup(virtual_address)

TLB[virtual_address] = physical_address

return fetch_data(physical_address)

Dieser einfache Mechanismus beschleunigt den Speicherzugriff erheblich. Tatsächlich können moderne CPUs Trefferquoten von über 99% bei ihren TLBs erreichen, was bedeutet, dass 99 von 100 Speicherzugriffen die langsamen Seitentabellen überhaupt nicht berühren müssen!

Die dunkle Seite: TLB-Fehler und Thrashing

Aber was passiert, wenn der TLB keine Übersetzung finden kann? Dies wird als TLB-Fehler bezeichnet und ist etwa so angenehm wie das Finden eines Fehlers im Produktionscode um 16:59 Uhr an einem Freitag.

Wenn ein TLB-Fehler auftritt, muss die CPU:

- Die Seitentabellen durchlaufen, um die richtige Übersetzung zu finden

- Den TLB mit der neuen Übersetzung aktualisieren

- Den Speicherzugriff erneut versuchen

Dieser Prozess kann schmerzhaft langsam sein, besonders wenn er häufig auftritt. Wenn Ihr Programm viele TLB-Fehler erlebt, kann die Leistung schneller sinken als ein Bleiballon. Dieser Zustand wird als TLB-Thrashing bezeichnet und ist der Albtraum für leistungssensitive Anwendungen.

Das Thrashing vermeiden

Um Ihre Programme reibungslos laufen zu lassen, beachten Sie diese Tipps:

- Verwenden Sie größere Seitengrößen, wenn es angebracht ist (große Seiten in Linux, große Seiten in Windows)

- Optimieren Sie Ihre Speicherzugriffsmuster für Lokalität

- Achten Sie auf die Größe Ihres Arbeitssatzes

Denken Sie daran: Ein glücklicher TLB ist ein leistungsfähiges Programm!

Über die Grundlagen hinaus: Fortgeschrittene Techniken des virtuellen Speichers

Wenn wir tiefer in das Kaninchenloch des virtuellen Speichers eintauchen, stoßen wir auf einige faszinierende fortgeschrittene Techniken:

Invertierte Seitentabellen

Traditionelle Seitentabellen können viel Speicher verbrauchen, insbesondere in 64-Bit-Systemen. Invertierte Seitentabellen drehen das Konzept um und verwenden eine Hashtabelle, um physische Seiten auf virtuelle Adressen abzubilden. Dies kann den Speicherbedarf der Seitentabellen erheblich reduzieren, allerdings auf Kosten potenziell längerer Suchzeiten.

Mehrstufige Seitentabellen

Um die großen Adressräume moderner Systeme zu handhaben, zerlegen mehrstufige Seitentabellen den Übersetzungsprozess in Stufen. Ein typisches x86-64-System könnte beispielsweise vier Ebenen von Seitentabellen verwenden:

CR3 → PML4 → PDP → PD → PT → Physische Seite

Dieser hierarchische Ansatz ermöglicht eine effiziente Speichernutzung und flexibles Speichermanagement.

ASID: Kontextwechsel ohne das Leeren

Adressraum-Identifikatoren (ASIDs) sind ein cleverer Trick, den einige Architekturen verwenden, um das Leeren des TLB bei jedem Kontextwechsel zu vermeiden. Indem TLB-Einträge mit einem ASID versehen werden, kann die CPU Übersetzungen von mehreren Prozessen gleichzeitig im TLB behalten.

struct TLBEntry {

uint64_t virtual_page_number;

uint64_t physical_page_number;

uint16_t asid;

// ... andere Flags

};

Dies kann die Leistung in Systemen mit häufigen Kontextwechseln erheblich verbessern.

Die Zukunft des virtuellen Speichers

Während wir die Grenzen des Rechnens erweitern, entwickelt sich der virtuelle Speicher weiter. Einige spannende Entwicklungen am Horizont umfassen:

- Heterogenes Speichermanagement: Mit dem Aufkommen von Systemen, die verschiedene Arten von Speicher (DRAM, NVRAM, HBM) kombinieren, passen sich virtuelle Speichersysteme an, um diese vielfältigen Ressourcen effizient zu verwalten.

- Hardware-unterstützte Seitentabellenläufe: Einige moderne CPUs enthalten spezielle Hardware für das Durchlaufen von Seitentabellen, was die Leistungseinbußen durch TLB-Fehler weiter reduziert.

- Maschinelles Lernen-gesteuertes Vorabrufen: Forscher untersuchen den Einsatz von ML-Techniken, um Speicherzugriffsmuster vorherzusagen und Seiten in den TLB vorab zu laden.

Zusammenfassung: Das unsichtbare Rückgrat der modernen Datenverarbeitung

Virtueller Speicher, mit seinem komplexen Zusammenspiel von Seitentabellen und TLBs, bildet das unsichtbare Rückgrat der modernen Datenverarbeitung. Es ist ein Zeugnis für die Genialität von Informatikern und Ingenieuren, die die Illusion von großen, zusammenhängenden Speicherbereichen aus fragmentierten physischen Ressourcen schaffen.

Das nächste Mal, wenn Ihr Programm läuft, denken Sie an die komplexe Maschinerie, die im Hintergrund arbeitet und Ihre unbeschwerten virtuellen Adressen in physische Realität übersetzt. Und denken Sie daran, in der Welt des virtuellen Speichers ist nichts so, wie es scheint – aber genau das macht es so mächtig.

"In der Informatik stehen wir auf den Schultern von Giganten – und diese Giganten stehen auf einer sehr cleveren Implementierung des virtuellen Speichers." - Anonymer Bit-Wrangler

Gehen Sie nun voran und allokieren Sie Speicher mit unbesorgter Hingabe – Ihr virtuelles Speichersystem hat Ihren Rücken!